The PCIe 4.0 specification was scheduled to be available late 2015, but as of now after the developers’ conference, the PCIe 4.0 specification is going to be available in early to mid 2016.

If you go back to 18 months before the PCIe 3.0 specification was supposed to be released, the PCI-SIG had almost another year delay. Back in September of 2011 I wrote about the need for PCIe roadmap to get into gear and go faster. Back then the PCI-SIG said that the specification would be available in 2015 or 2016.

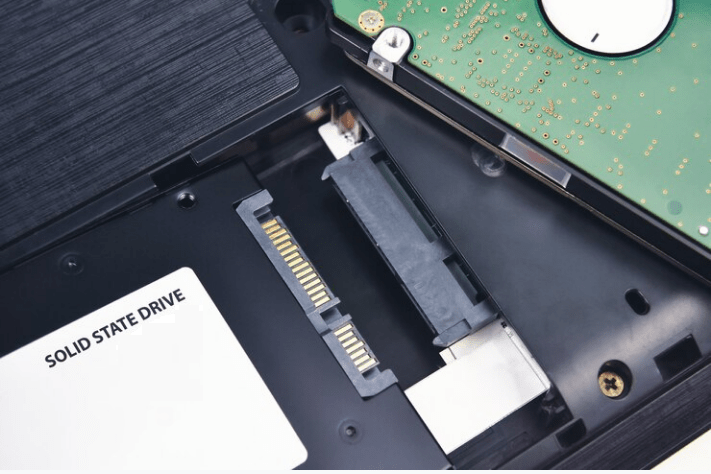

The issues are still that we are only expecting a total 8x improvement over the initial PCIe 1.0 specification in 12 years (2004 to 2016 for product, if they are on time with the specification in 2016).

Let’s make some reasonable assumptions based on the past. PCIe 4.0 specification will be out maybe 6 months late and products will be available 4 months later. This is similar to PCIe 2.0 and 3.0 lateness and availability.

So that means we can see PCIe 4.0 products in late 3Q16 or early 4Q16. This will be in time for 24 Gbit/sec SAS, but PCIe 4.0 will be very late for EDR InfiniBand and host side 100 Gbit ethernet. It’s easy, of course, for me to say just get it done, but these are hard problems.

You have to integrate the PCIe channel such so that there is connectivity to memory to supply enough bandwidth. Today that number is 40 GB/sec and with PCIe 4.0 that will likely go to 80 GB/sec. Heck it was not but a few years ago that the memory bandwidth of a whole Xeon was less than 80 GB/sec, but as I have always said the issue is a balanced system. CPU performance has gone up, memory bandwidth has gone up both more than 8x since 2004, while I/O bandwidth in and out of the system has not. 80 GB/sec per bus is not going to be enough.